基于FPGA的出租车计价器实现

基于FPGA的出租车计价器实现(任务书,开题报告,论文12000字)

摘 要

随着EDA技术的迅猛发展,电子系统的相关设计技术已经发生了重大变化。大规模可编程逻辑器件CPLD/FPGA的出现,给我们带来了诸多便利。利用它进行产品开发,不仅周期短、成本低、可靠性高、灵活性高,而且具有完全的自主知识产权。

本文介绍了一个以Altera公司生产的可编程逻辑芯片cyclone2系列的EP2C5T144C8的FPGA芯片为核心,外加一定的外围电路组成的出租车计价器系统设计。本次设计使用Verilog HDL硬件描述语言设计出租车计价器,并通过QuartusⅡ软件进行编译、仿真等,然后下载到FPGA芯片中。本次设计利用LCD1602液晶显示屏动态显示停车等待时间,行驶总里程,总费用(包括白天和黑夜)。

由于FPGA具有密度高、可编程、软件支持强等特点,所以本计价器功能强、灵活性高、可靠性高,具有一定的实用价值。

关键词:FPGA VerilogHDL QuartusⅡ LCD1602

The Taxi Meter Design Based On FPGA

Abstract

With the rapid development of EDA technology, the design technology of electronic system has undergone significant changes. The large-scale programmable logic device CPLD/FPGA, brought us many conveniences. Use it for product development, not only the short cycle, low cost, high reliability, and has full intellectual property rights. [资料来源:http://doc163.com]

This paper introduces a FPGA chip produced by Altera company cyclone2 series programmable logic chip EP2C5T144C8 as the core, and peripheral circuit of taximeter system. This design uses the Verilog HDL hardware description language to design taximeter, compile, simulation in Quartus software, and then downloaded to the FPGA chip. In this paper, using the LCD1602 LCD screen dynamic display of waiting time, total length of road, the total cost (both day and night). Because FPGA has the characteristics of high density, programming, software support is strong, so the valuation of strong function, high flexibility, high reliability, and has a certain practical value.

Keywords:FPGA;Verilog HDL;QuartusⅡ;LCD1602

[版权所有:http://DOC163.com]

目录

摘 要 Ⅰ

ABSTRACT Ⅱ

第一章 绪论 1

1.1 研究意义及研究现状 1

1.1.1研究意义 1

1.1.2研究现状 1

1.2 EDA设计概述 2

1.3 论文主要工作 5

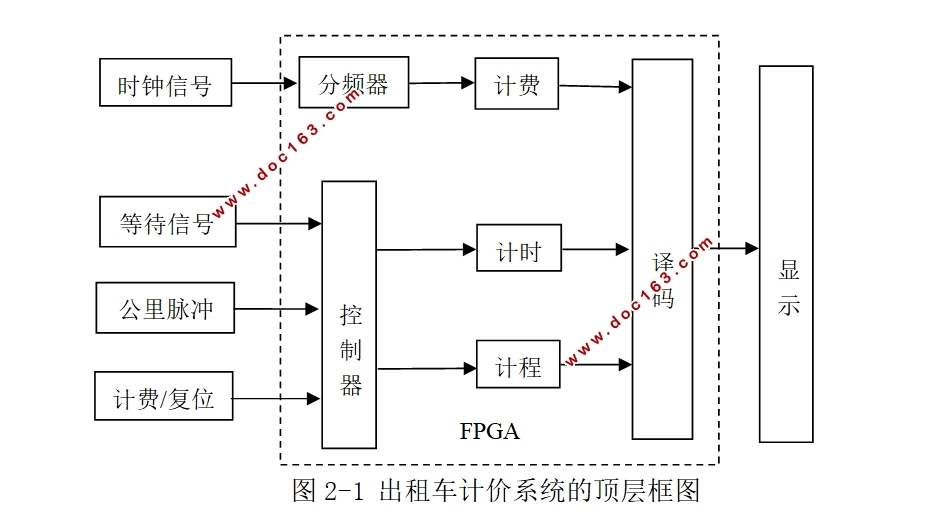

第二章 系统总体设计 6

2.1设计要求 6

2.2系统整体框图 6

2.3出租车计价器流程图 7

第三章 系统硬件电路设计 8 [资料来源:Doc163.com]

3.1 各功能电路的设计 8

3.1.1 FPGA最小系统 8

3.1.2显示模块 9

3.1.3 按键模块 10

3.1.4 拨码开关模块 10

3.1.5下载模块 11

3.1.6电源 11

3.2 PCB板设计 11

第四章 软件设计及仿真 13

4.1 软件设计 13

4.1.1时钟分频模块 13

4.1.2计程模块 14

4.1.3实时时钟模块 15

4.1.4等待时间模块 15

4.1.5计价模块 17

4.1.6译码和显示模块 18

4.1.7清零模块 21

4.1.8按键去抖模块 22

4.1.9顶层模块 23

4.2系统仿真 24

4.2.1时钟分频模块 24

4.2.2计程模块 24

4.2.3实时时钟模块 25

4.2.4等待时间模块 26 [版权所有:http://DOC163.com]

4.2.5计价模块 27

第五章 硬件验证 29

第六章 总结和展望 31

6.1 总结 31

6.2 展望 32

参考文献 33

致谢 35 [资料来源:https://www.doc163.com]