基于FPGA和锁相环的信号发生器的设计

基于FPGA和锁相环的信号发生器的设计(论文14000字)

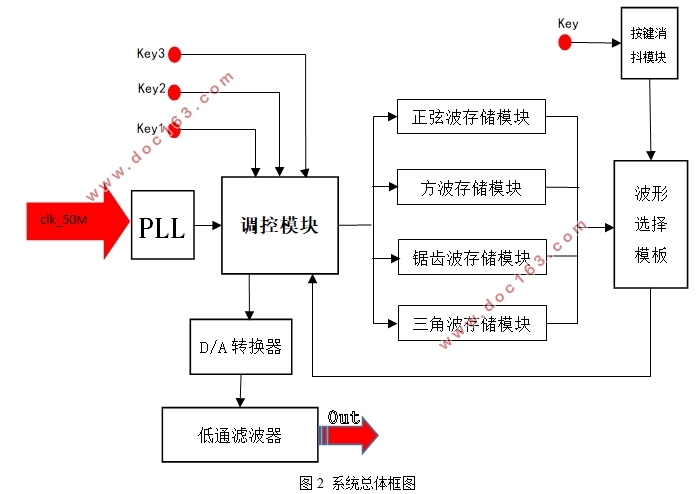

摘要:与传统信号发生器相对比,利用FPGA技术来设计的DDS电路系统具有更为突出的优势。本文的主要研究内容是基于FPGA和锁相环的可调信号发生器的设计与实现。本文采用的FPGA器件是Altera公司的CycloneⅣ系列产品EP4CE15F17C8N,在QuartusⅡ环境下以硬件描述语言Verilog HDL为开发手段,结合锁相环和DDS技术的原理设计了一款可以产生正弦波、方波、锯齿波和三角波的信号发生器,四种信号之间不仅可以任意切换而且还可以调控输出信号的频率、相位和幅度,并给出了相应的仿真结果和调试结果。本文设计的信号发生器有设计灵活、成本功耗低、频率稳定性和准确度高等优点。

关键词:FPGA;锁相环;信号发生器;Verilog HDL

Design and Implementation of Signal Generator

Based on FPGA and Phase - locked Loop

Abstract:Compared with the traditional signal generator, the DDS circuit system designed with FPGA technology has more prominent advantages. The main research content of this paper is the design and implementation of an adjustable signal generator based on FPGAand PLL. The FPGA device used is the Altera company's Cyclone IV series EP4CE15F17C8Nin this paper.With hardware description language Verilog HDL as development toolsin Quartus II, according to the principle of PLL and DDS technology to design a signal generator which can produce sine wave,square wave, sawtooth wave and triangular wave. Four kinds of signal not only canbe switched arbitrarily, but also the frequency, phase and amplitude of the output signal can be adjusted, and the corresponding simulation results and debugging results are given. The signal generator designed has the advantages of flexible design, low cost, low power consumption, high frequency stability and high accuracyin this paper. [资料来源:www.doc163.com]

Key words: FPGA; Phase-locked loop; Function generator; VerilogHDL

[资料来源:www.doc163.com]

目 录

1绪论 1

1.1课题的背景和意义 1

1.2国内外研究现状 1

1.3论文的主要工作内容 2

2总体方案设计 2

2.1信号发生器简介 2

2.2设计方案分析 2

2.3系统总体设计 3

3基于FPGA和锁相环的信号发生器的设计 4

3.1开发环境及相关技术 4

3.1.1 FPGA及其开发流程 4

3.1.2 开发环境 5

3.2锁相环模块 6

3.2.1锁相环的作用 6

3.2.2锁相环的基本原理 6

3.2.3锁相环设计 6

3.3 调控模块 7

3.3.1调控模块简介 7

3.3.2相位计数模块 8

3.3.3调控模块结构 8

3.4波形数据ROM模块 9

3.4.1 波形数据ROM模块工作原理 9

3.4.2设计步骤 9

3.5按键消抖 10

3.5.1按键消抖工作原理 10

3.5.2按键消抖模块设计 11

3.6波形选择模块 11

3.6.1波形选择模块 11

3.6.2波形选择模块设计 11

3.7顶层原理图及仿真 12

3.7.1顶层原理图 12

3.7.2仿真测试 12

3.8 D/A转换器 15

3.8.1 AD9708芯片简介 15

3.8.2 AD9708芯片与FPGA的连接 16 [来源:http://Doc163.com]

4硬件配置与系统调试 16

4.1 FPGA的配置 16

4.2 JTAG配置 17

4.3系统调试 17

5结论 18

参考文献 19

致 谢 20

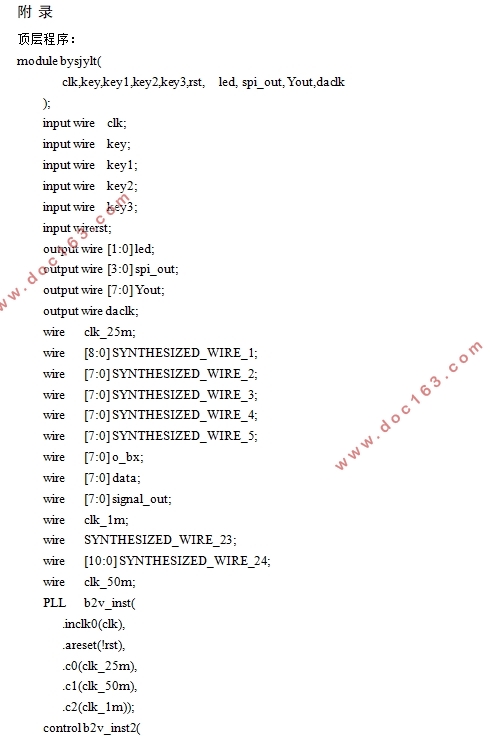

附 录 21 [资料来源:http://www.doc163.com]