QC-LDPC码的编码理论及FPGA实现(FPGA,Matlab)

资料介绍:

QC-LDPC码的编码理论及FPGA实现(FPGA,Matlab)(任务书,开题报告,外文翻译,论文说明书10600字,FPGA,Matlab)

摘要

LDPC码最初在1963 年Gallager博士论文中提出,是具有稀疏校验矩阵的线性分组码,拥有接近Shannon极限的优异性能。但限于当时硬件技术的限制,没有得到足够的重视。英国的 Mackay教授等人在1996年“再发现”LDPC码后,LDPC码才受到了学术界和应用界的广泛关注,掀起了信道编码界的研究热潮。伴随着现在硬件技术的发展,LDPC 码已经被广泛应用于第四代移动通信系统、卫星通信、网络编码协作通信系统、CMMB 等通信系统中。QC-LDPC码是LDPC 码的一个子类,具有准循环特性,有关学者和专家研究出了基于SRAA结构的编码器,大大降低了编码复杂度,降低了对硬件资源的消耗,并在一定程度上保持了性能的优势。

本文首先在线性分组码的基础上介绍了LDPC码的基础理论,比较检验矩阵的随机化和结构化的构造方法,重点对准循环构造法进行认真研究。

然后针对不同参数组合下构造出的检验矩阵进行Matlab性能仿真和对比,选出最优的参数组合下的校验矩阵。

最后,基于 Quartus II 14.1软件,利用 verilog HDL 语言实现了QC-LDPC码编码器的布局布线以及综合优化。使用 Modelsim 10.0进行了仿真测试成功完成QC-LDPC编码器的各个模块的FPGA实现。

[资料来源:https://www.doc163.com]

关键词:QC-LDPC码;SRAA结构;Matlab性能仿真;FPGA

Abstract

LDPC codes, first in Gallager in 1963 doctoral thesis, is a sparse parity check matrix of linear block codes, which have excellent performance approaching Shannon limit. But limited to restrictions of the hardware technology, we did not get enough attention. British Professor Mackay in 1996 "re-discovered" LDPC codes, LDPC codes only been widespread concern academia and industry applications, setting off a wave of research channel coding community. With the current development of hardware technology, LDPC codes have been widely applied to the fourth generation mobile communication systems, satellite communication, network coding cooperative communication systems, CMMB and other communication systems. QC-LDPC code is a subclass of the LDPC codes, which has a quasi-cycle characteristics. Scholars and experts developed a coder based SRAA structure, greatly reduced the coding complexity, reduced hardware resource consumption, and to some extent maintained a performance advantage.

[资料来源:http://Doc163.com]

Firstly, based on a linear block code introduces the basic theory of LDPC codes constructed random and structured comparison test matrix, careful research priorities aligned loop construct method.

Then Matlab simulation and performance comparison for different parameter combinations constructed test matrix, select the check matrix under the optimal combinationof parameters.

Finally, based on Quartus II 14.1 software using Verilog HDL language of the QC-LDPC code encoder and integrated layout optimization. Use Modelsim 10.0 simulation test, the successful completion of each module FPGA QC-LDPC encoder implementation.

Key Words:LDPC codes;SRAA structure;Matlab simulation;FPGA

本文的主要研究目的是:

1.了解LDPC码及QC-LDPC码的基本理论;

2. 研究校验矩阵的随机化构造法和结构化构造法,尤其是准循环构造法;

3. 学习基于Matlab的检验矩阵的性能仿真;

4. 选出最优的参数组合下的校验矩阵;

5. 学习FPGA对QC-LDPC编码实现

[资料来源:https://www.doc163.com]

目 录

第1章绪论 1

[资料来源:www.doc163.com]

1.1 数字通信系统 1

1.2 信道编码技术的发展历程 2

1.3 LDPC码的研究现状 3

1.4 研究的目的及意义 4

1.5 本文研究内容安排 4

第2章 LDPC码的编码原理 6

2.1 LDPC码的定义及表示方法 6

2.2 LDPC码的主要构造方法 8

2.2.1 随机化构造方法 8

2.1.2 结构化构造方法 10

2.3 QC-LDPC码的基本概念 11

第3章 QC-LDPC码的编码性能仿真 12

3.1 二进制QC-LDPC码编码的Matlab实现 12

3.2 几种常见的QC-LDPC码性能仿真 13

3.3 不同码长的QC-LDPC码 14

第4章 QC-LDPC码的FPGA仿真实现 16

4.1 FPGA简介 16

4.2 QC-LDPC码编码器总体结构 16

4.3 编码模块的设计 17

4.3.1 单编码器的设计 17 [来源:http://www.doc163.com]

4.3.2 单编码器的级联 18

4.4 控制模块设计 20

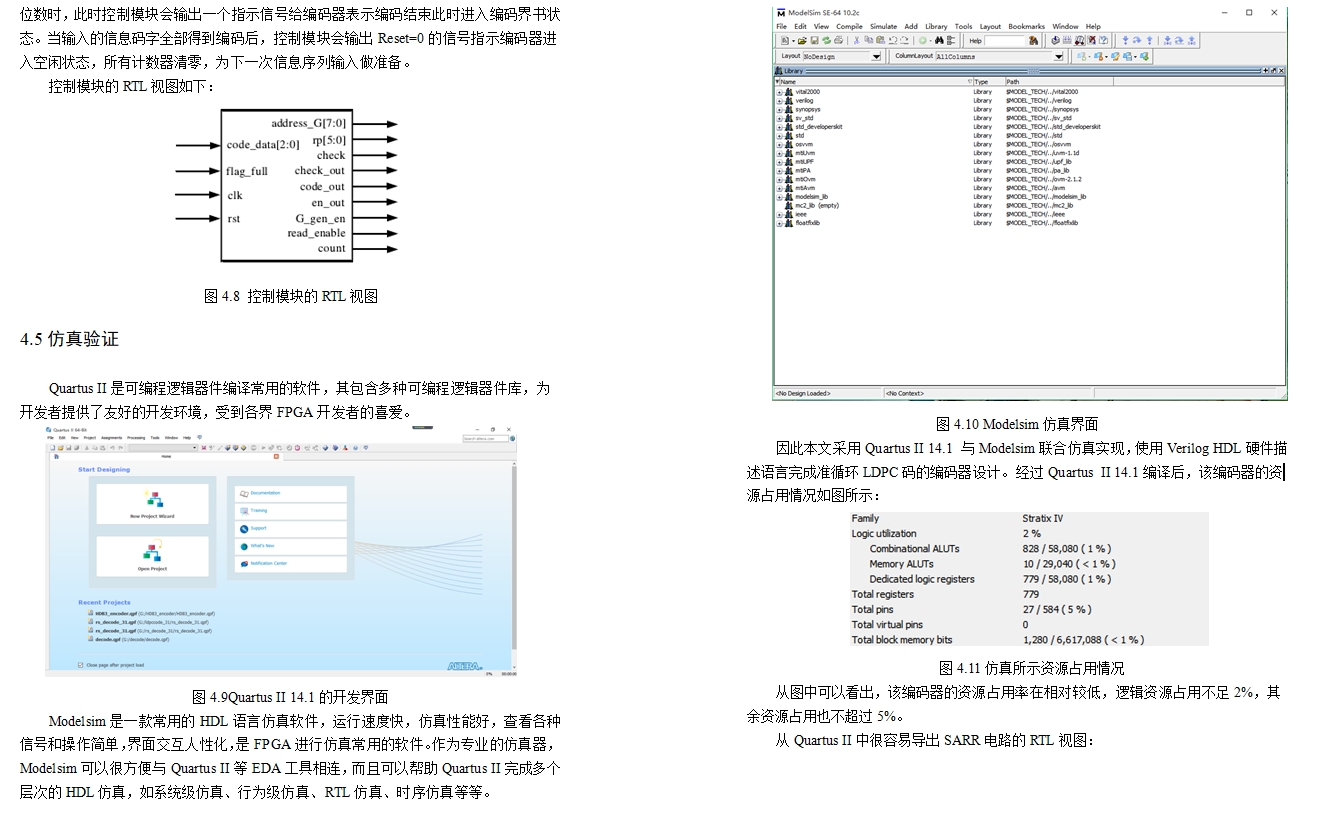

4.5 仿真验证 21

第5章总结 25

参考文献 26

致谢 27

[来源:http://Doc163.com]