一种基于FPGA的信号源设计(附程序清单)

一种基于FPGA的信号源设计(附程序清单)(论文16000字)

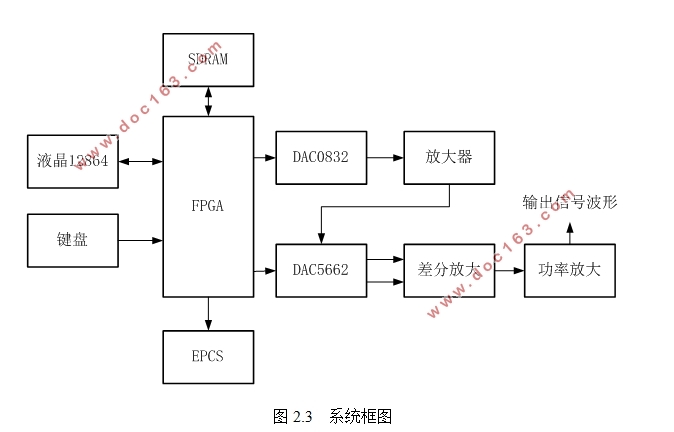

摘要:本设计从实际出发,在传统信号源普遍存在体积过大,能耗太大,价格高昂的情况下,针对实验研究设计出一款结构紧凑、性能稳定、低功耗多功能的信号发生器。该信号发生器可以输出三种波形,分别为正弦波信号、三角波信号、方波信号,幅度在0~5V范围内可控,频率在1Hz~1MHz范围内可控。本设计主要采用FPGA技术,利用VHDL语言进行编程完成,应用DDS设计原理,在FPGA上实现DDS的功能,同时在FPGA上采用SOPC技术实现控制系统。本设计在教学和科研中有很多积极意义。

关键字:FPGA;信号发生器;DDS;SOPC

Design of an FPGA-based signal generator

Abstract: The design is considered from the reality, in the condition of conventional signal generators having too large volume , and too high price, consuming too much energy, design a compact, stable performance, low-power multi-function signal generator device targeted at laboratory environment. The signal generator can output sine, triangle, square wave three waveforms, amplitude range of 0 to 0 ~ 5V, the frequency range of 1Hz ~ 1MHz. This design uses FPGA technology, uses VHDL language programming to complete, applies the design principles of DDS to achieve DDS functions on FPGA, at the same time, uses SOPC technology control systems on FPGA. This design has a lot of positive significance in teaching and research fields. [资料来源:https://www.doc163.com]

Key words: FPGA; Signal generator;DDS;SOPC

[资料来源:Doc163.com]

目 录

1 绪论 1

1.1 论文研究背景以及意义 1

1.2 论文的研究内容和研究目标 1

2 设计指标以及方案 1

2.1 信号发生器的技术指标 1

2.2 方案论证和设计 2

2.2.1 设计思路 2

[资料来源:http://doc163.com]

2.2.2 方案设计 2

2.2.3 方案确立与系统整体结构体 3

3 设计原理 4

3.1 直接数字频率合成(DDS)的原理 4

3.1.1 DDS简介 4

3.1.2 DDS的基本原理 4

3.2 FPGA简介以及VHDL程序的特点 5

3.3 DDS在FPGA中的实现 5

4 系统硬件设计 6

4.1 FPGA部分设计 6

4.1.1 FPGA类型的选择 6

4.1.2 FPGA对DDS电路的具体实现 6

4.1.3 FPGA对SOPC的接口通信设计 7

4.2 电源模块设计 7

4.3 键盘模块设计 8

4.4 显示模块设计 9

4.5 D/A转换部分设计 9

4.5.1 DAC0832电路设计 9

4.5.2 DAC5662电路设计 10

4.6 功率放大电路设计 12

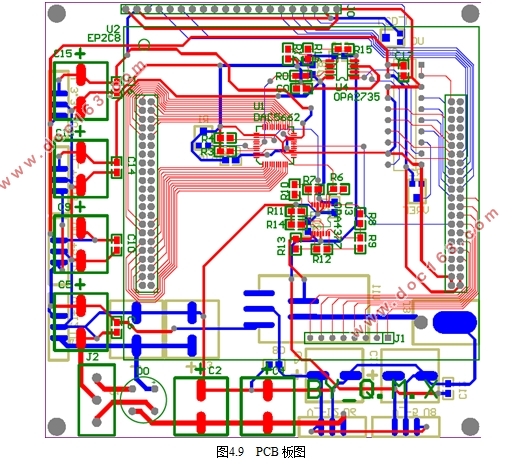

4.7 系统PCB设计 12

[资料来源:http://doc163.com]

5 系统软件设计 13

5.1 开发环境介绍 13

5.1.1 QUARTUS II软件介绍 13

5.1.2 NIOS II IDE软件介绍 14

5.1.3 MATLAB软件介绍 14

5.2 FPGA的软件设计 14

5.2.1 系统时钟源的软件设计 14

5.2.2 键盘模块的软件设计 15

5.3 SOPC的软件设计 16

5.3.1 LCD显示模块的软件设计 17

5.3.2 数据处理模块的软件设计 17

5.3.3 EPCS程序存储的软件设计 18

5.3.4 MATLAB查找表设计 18

6 系统调试与测试 20

6.1 系统硬件调试 20

6.2 系统软件调试 20

6.3 系统测试与误差分析 21

7 总结 24

参考文献: 24

致谢 26

附录 27

[来源:http://Doc163.com]

上一篇:基于FPGA的高精度电子罗盘设计